<u>osana@eee.u-ryukyu.ac.jp</u>

Reconfigurable architecture #2

#### This and next week

- \* Basics of Verilog HDL

- Language to program logic circuit

- Simulator: to verify behavior in waveform

- Synthesis tool: generates equivalent circuit in gate-level

### Module and port

- In HDL, behavior is described per module basis

- Module has "ports" to connect outside

- A port is like a terminal

- From outside, we can't see inside a module

- A module can contain submodules (as blackbox)

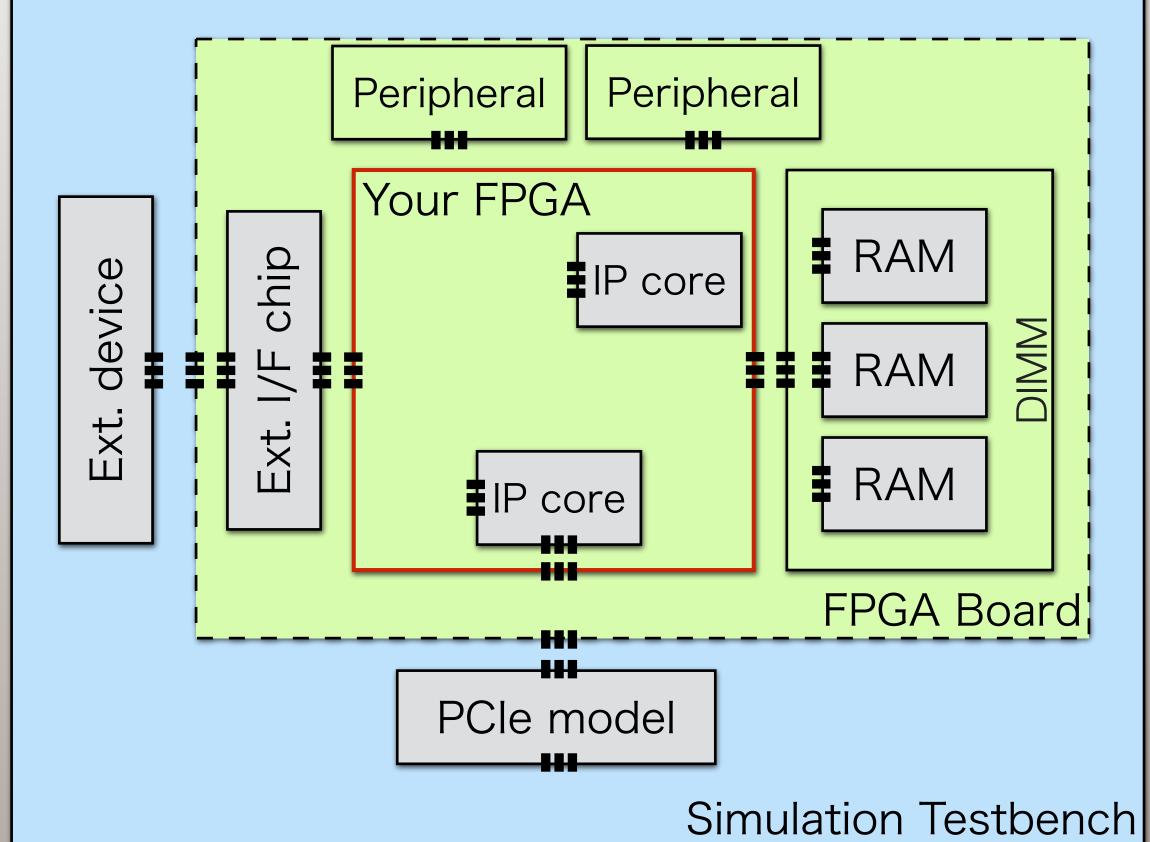

### **Everything as modules**

- \* FPGA design include

- Your HDL module + IP cores (imported design)

- External device models in testbench

### **Tools and HDL syntax**

- Not all of HDL syntax is "synthesizable"

- Some syntax is valid only for simulation

- Used in testbench (we'll see in later class)

- At least, FPGA part must be written in "synthesizable" form

# Writing HDL

- Verilog HDL or VHDL

- \* "Logic circuit in gate level" is possible, but too hard

- "Writing RTL behavior" is easier and common

- RTL = Register Transfer Level

- C/C++/Java is becoming popular

More recently, high-level synthesis (HLS) to generate RTLs from

#### Gate level

- Composed by "NAND", "Flip-flop" or that kind of...

- Or, obtained from RTL by "Logic synthesis"

Must be optimized manually: Not realistic for large circuits

# **RTL description**

- Do what if received this signal in this state

- Programmer can give any (meaningful) name to signals

- assignments

- No details about the final gate-level circuit is required

#### Some "software-like" syntax as "if" statement or conditional

#### HDL as a programming language

- \* HDL is uncommon as a programming language

- Programming language is usually about software

- Executed in "up-to-down" manner

- \* HDL describes components, continue working all the time

- No beginning or end in HDL world!

# Logic synthesis

- Optimal design for each device technology

- \* NAND gates are not almighty

- - Synthesis tools maps RTL to the logic cell libraries

- \* HDL is (basically) common to all device technologies

#### \* Every LSI process and every FPGA have different logic cells

### How to learn HDL

- Syntax: basically same to logic circuit

- Combinational and sequential logic

- \* HDL specific stuff:

- Module hierarchy and simulation

- ··· and system organization is much more difficult

#### Schedule

- \* Episode 1: Module, Combinational circuit and Operators

- \* + Design constraints

- Episode 2: Sequential logic and Hierarchical design

- Episode 3: Simple testbench and Running simulation

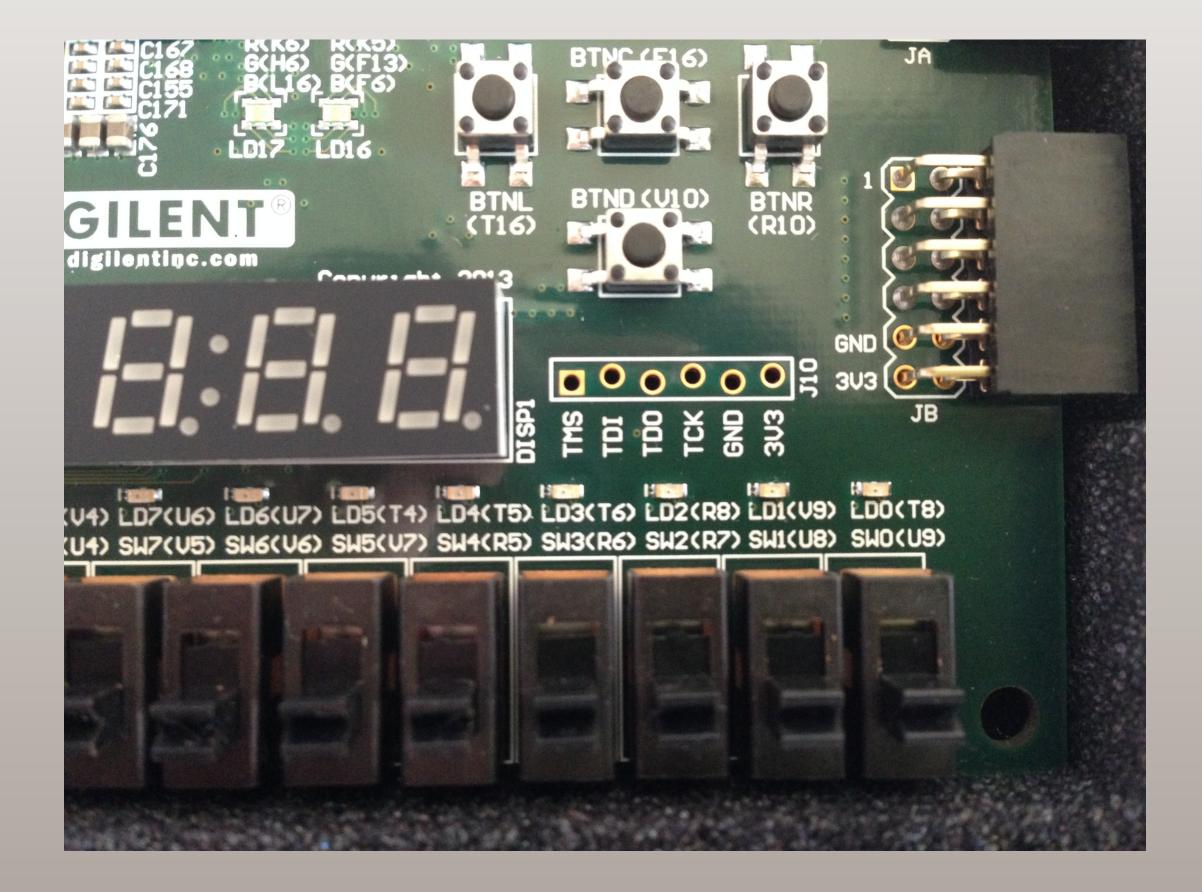

### Goal of the day

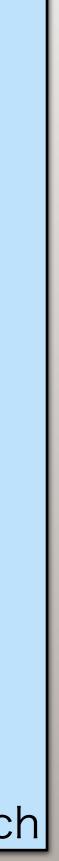

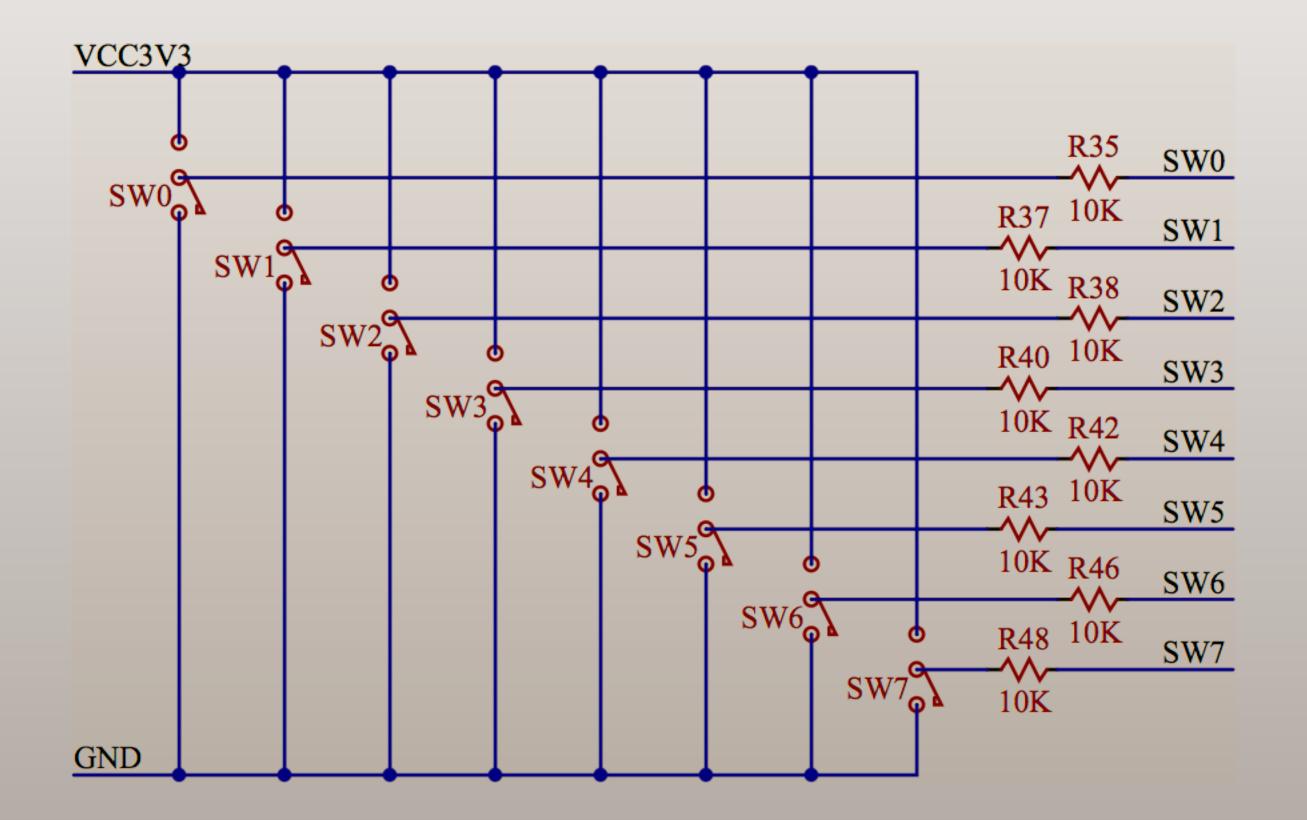

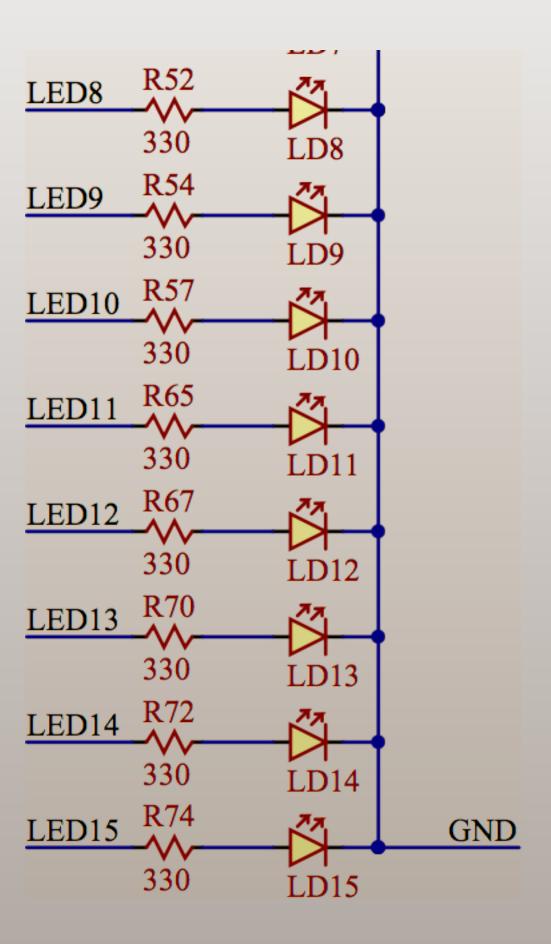

- LEDs and slide SWs

- With logic gates intermediate

- \* 16 LEDs and SWs on board

- Also try using push SW

- First of all, let's see the syntax

#### Literals

- 123: "Normal" numbers are interpreted as a (32bits) decimal

- 32'h1248abcd : Hexadecimal "1234abcd" of 32bits

- b: binary, d: decimal, h: hexadecimal

- Inserting "\_" between any columns is allowed for better readability \*

- example: 32'h1234\_abcd \*

- Single bit of "1" means "True", "0" is "False" \*

- Vector signal is "False" if all bits are 0

### Module and port

- Module definition

- starts by "module"

- \* ends by "endmodule"

- \* endmodule has no ";"

#### module module\_name ( ports );

. . .

endmodule

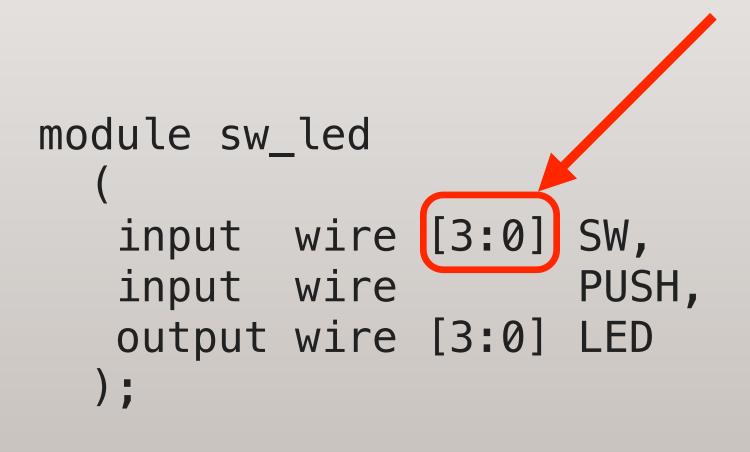

### Module and port

#### Signal has 4 bits, LSB is numbered as "0"

. . .

endmodule

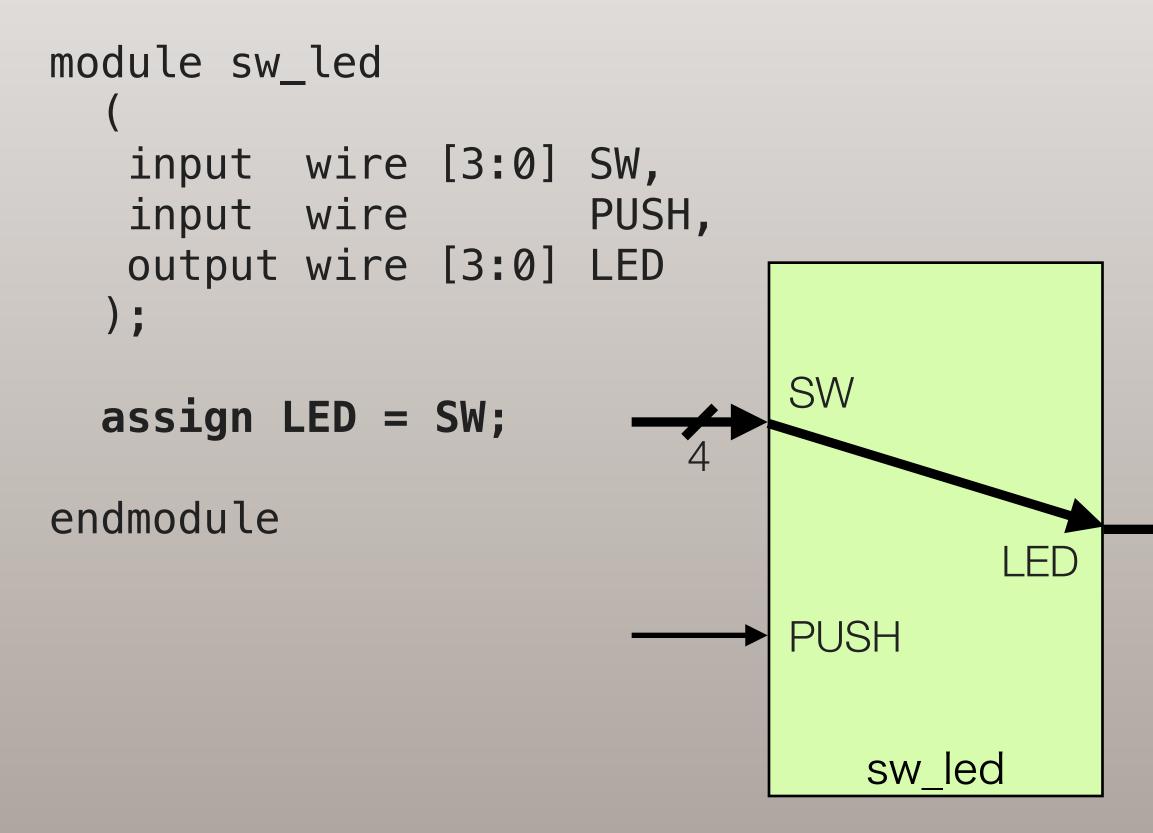

# Continuous assignment

- Assignments in software:

- Happens when executed

- In hardware:

- Happens continuously (because it's wired)

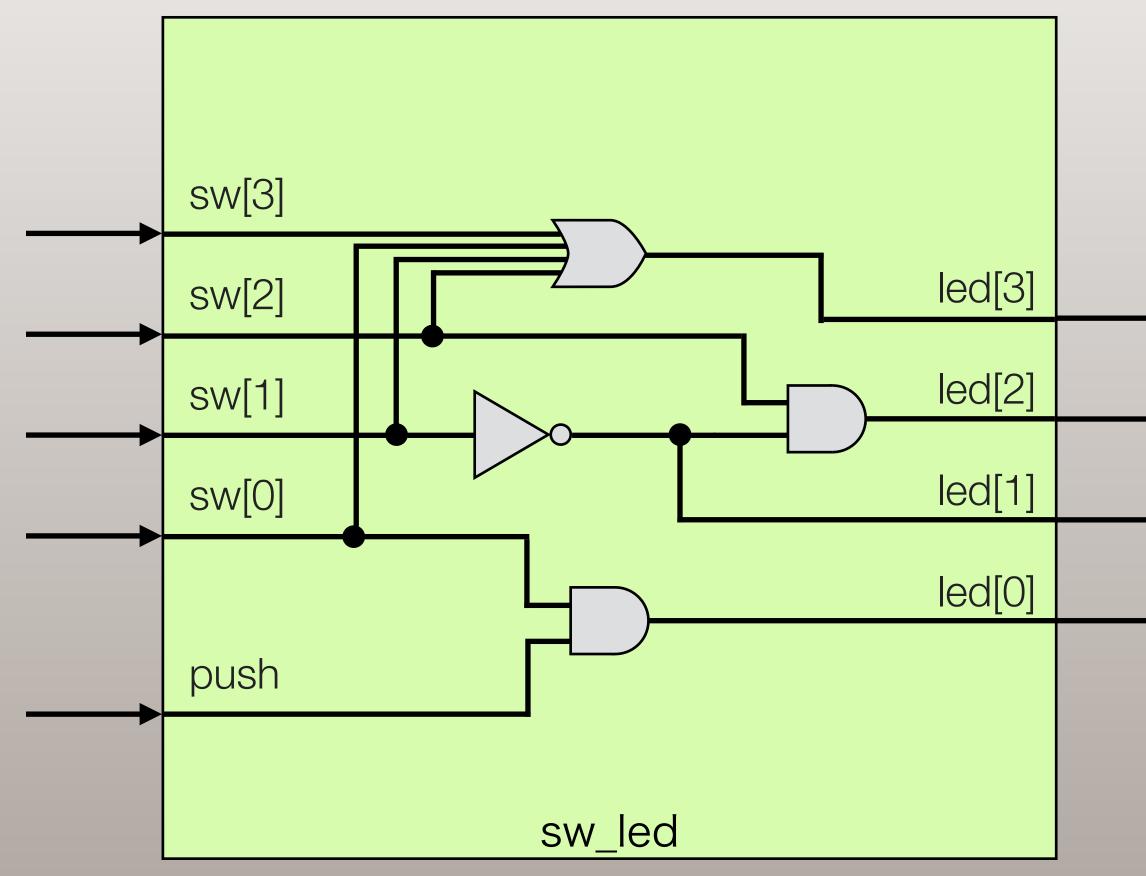

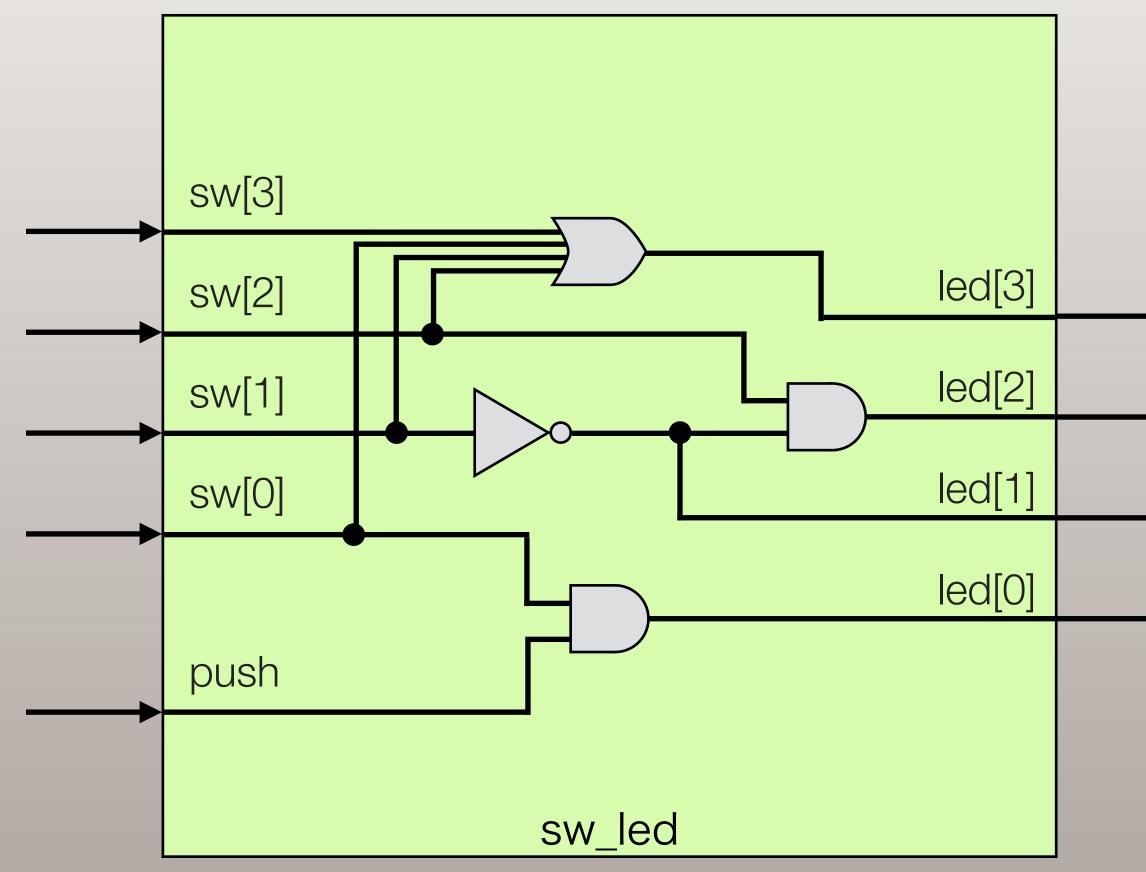

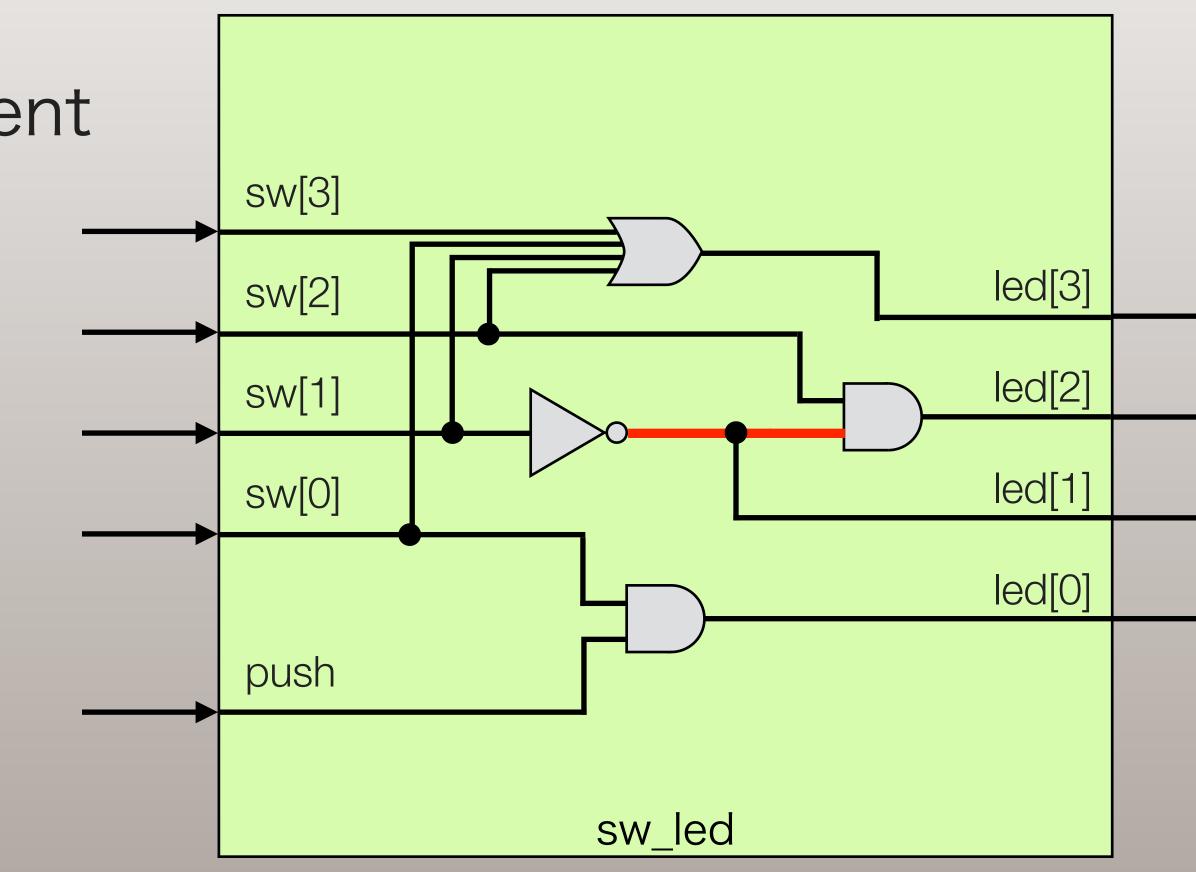

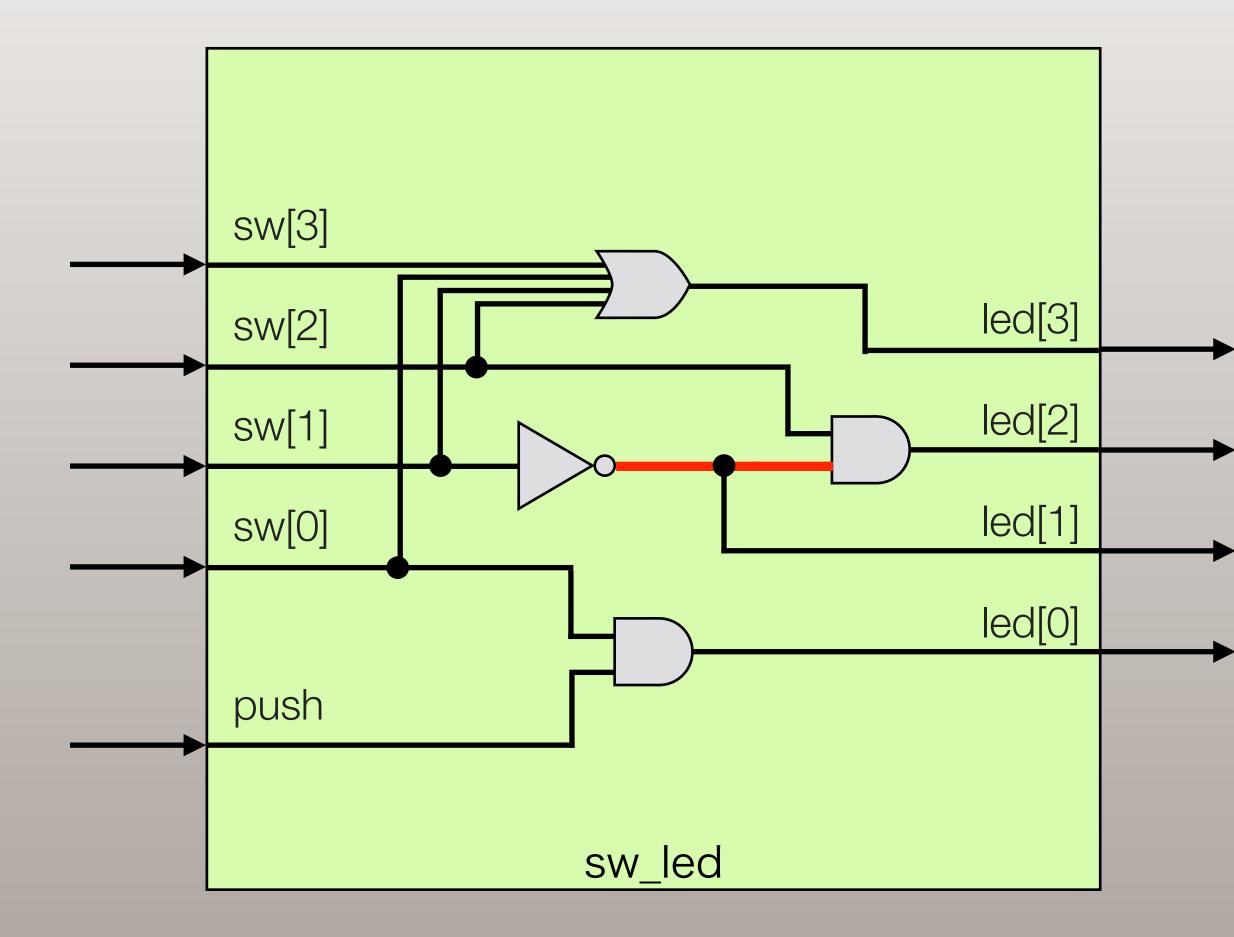

# Ex1: Basic logic gates

#### \* AND, NOT, OR gates

### Logic operators

#### \* AND: "&", OR: "|", NOT "~"

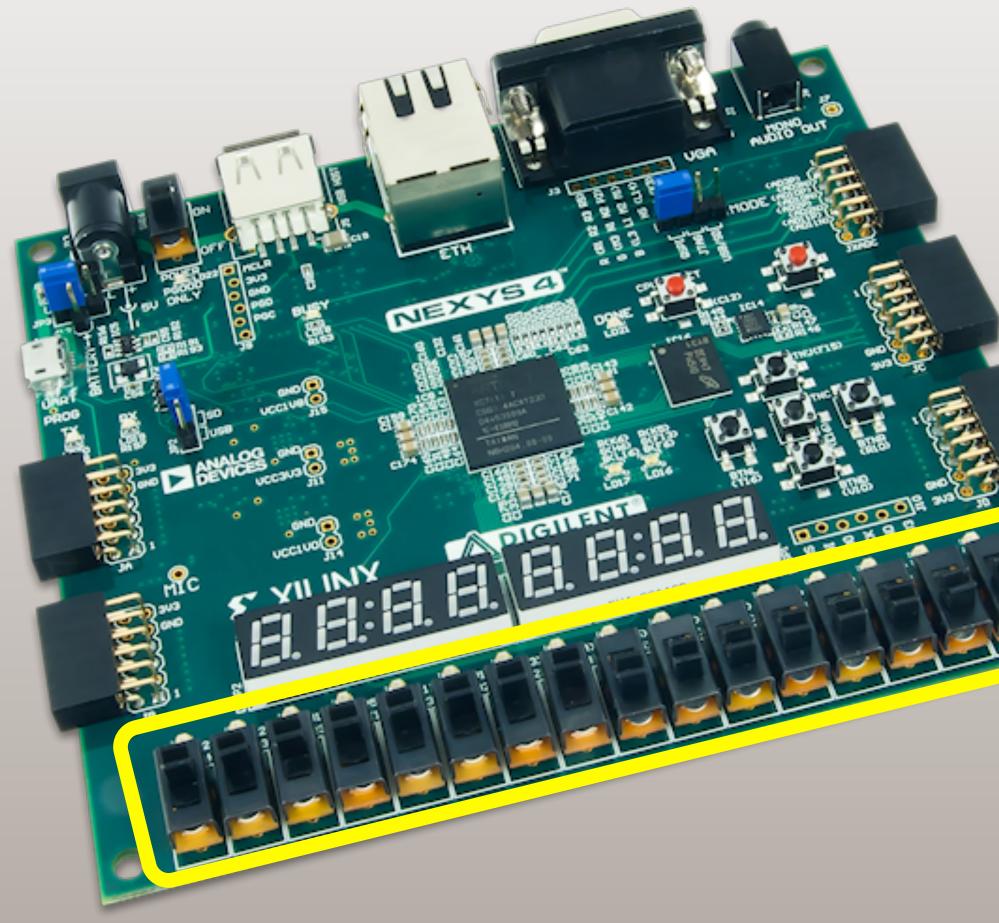

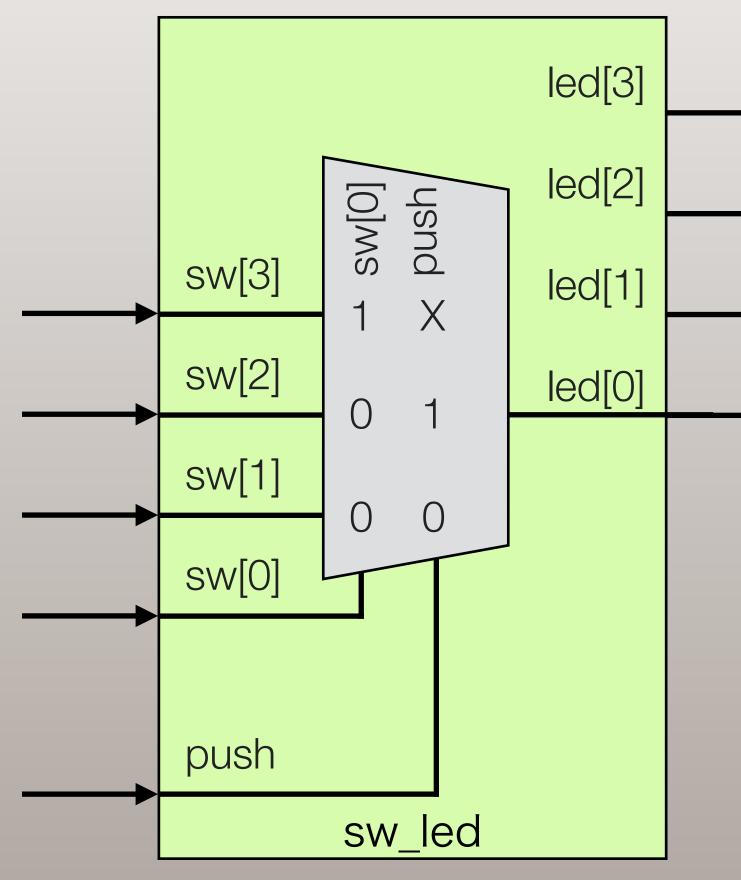

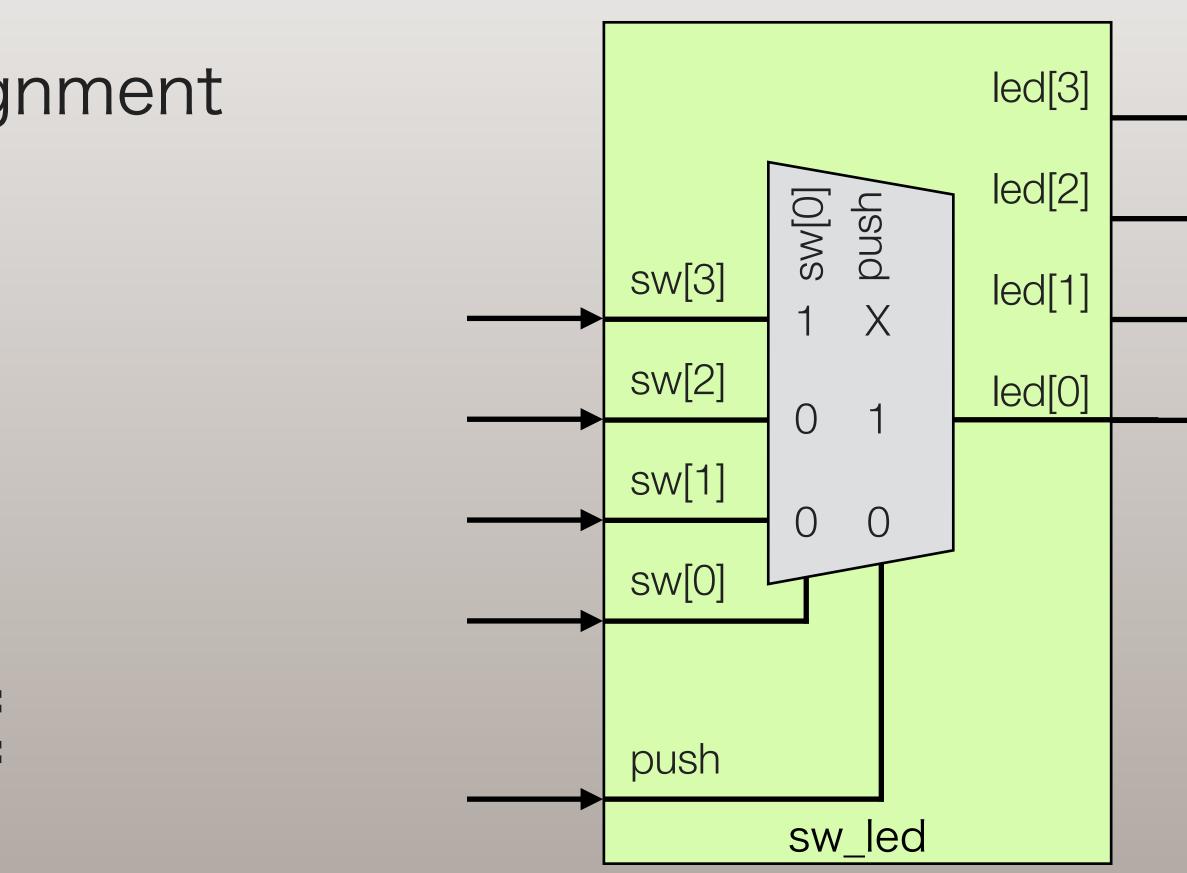

module sw\_led

(

input wire [3:0] SW,

input wire PUSH,

output wire [3:0] LED

);

assign LED[0] = PUSH & SW[0];

assign LED[1] = ~SW[1];

assign LED[2] = LED[1] & SW[2];

endmodule

#### Name internal signals

\* "wire" type for assign statement

```

module sw_led

input wire [3:0] SW,

input wire PUSH,

output wire [3:0] LED

);

wire

SW1_;

assign SW1_ = \simSW[1];

assign LED[1] = SW1_;

assign LED[2] = SW1_ \& SW[2];

```

endmodule

### Name internal signals

Assignment can be done within wire declaration

```

module sw_led

input wire [3:0] SW,

input wire PUSH,

output wire [3:0] LED

);

wire SW1_;

assign SW1_ = ~SW[1];

assign LED[1] = SW1_;

assign LED[2] = SW1_ \& SW[2];

```

endmodule

```

module sw_led

input wire [3:0] SW,

input wire PUSH,

output wire [3:0] LED

);

wire SW1_ = \sim SW[1];

assign LED[1] = SW1_;

assign LED[2] = SW1_ \& SW[2];

```

endmodule

#### Reduction operator

- \* LED[3]: Simplify or'ing call

- Operator before signal

```

module sw_led

(

input wire [3:0] SW,

input wire PUSH,

output wire [3:0] LED

);

```

```

assign LED[3] = |SW;

```

```

endmodule

```

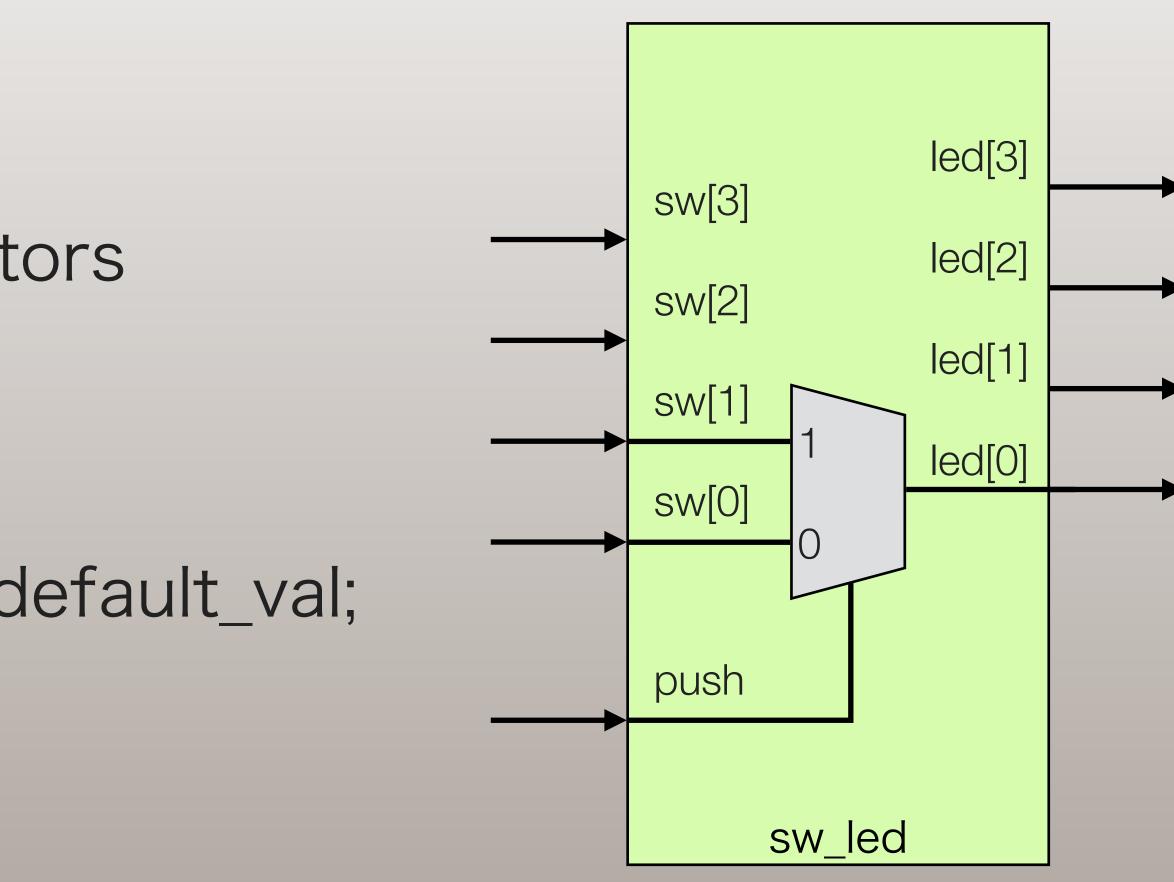

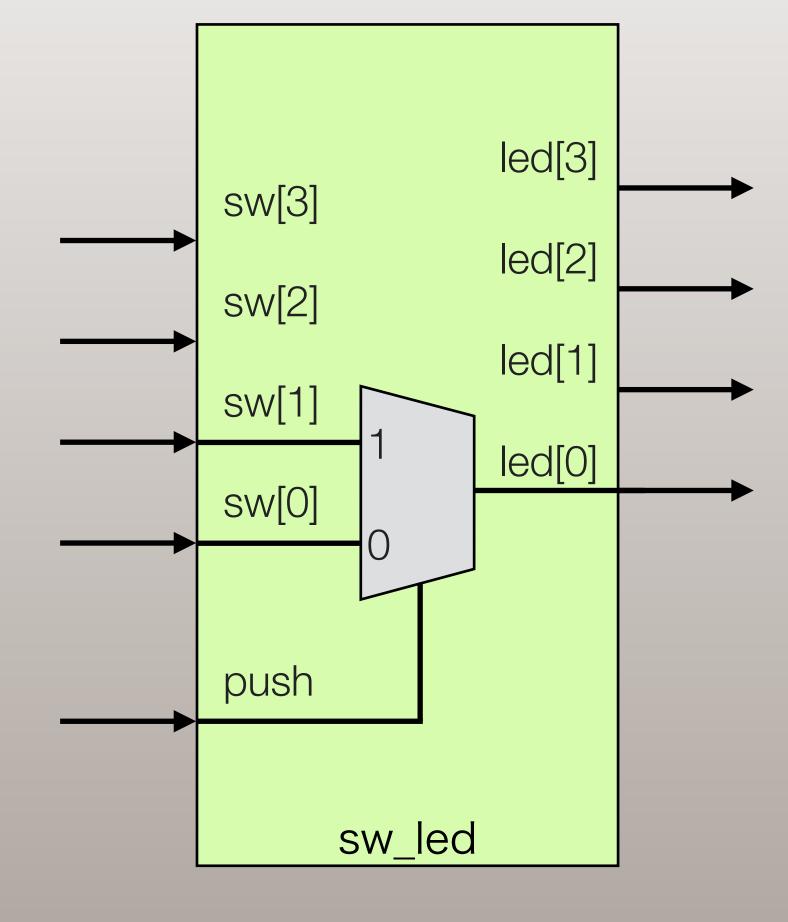

### Ex2: Multiplexer

- 2-input MUX

- Not simple with logic operators

- Conditional assignment

- \* assign X = (cond) ? value : default\_val;

- Don't forget default value

### Ex2: Multiplexer

- Conditional assignment

- \* assign X = (cond) ? val : default\_val;

```

module sw_led

input wire [3:0] SW,

input wire

PUSH,

output wire [3:0] LED

);

```

assign LED[0] = PUSH ? SW[1] : SW[0];

endmodule

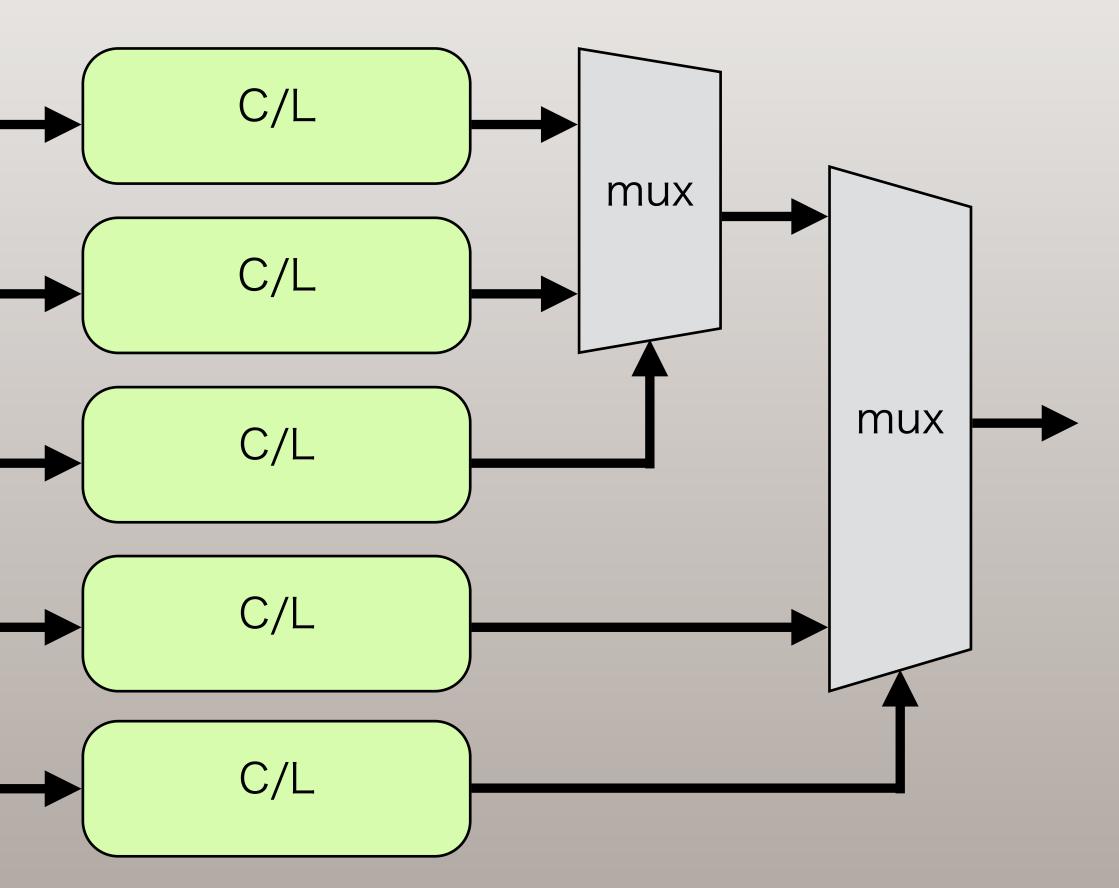

### Ex2.5: Multi-input MUX

#### 2bit select signal

# Signal decomposition and concatenation

- \* [] to extract bit(s)

- \* {} to concatenate

- New "bundled" signal

- Duplication:

{4{X}} is { X, X, X, X }

```

module sw_led

(

input wire [3:0] SW,

input wire PUSH,

output wire [3:0] LED

);

wire [1:0] SEL;

assign SEL = { SW[0], PUSH };

```

endmodule

### Ex2.5: Multi-input MUX

Possible with conditional assignment

```

module sw_led

(

input wire [3:0] SW,

input wire PUSH,

output wire [3:0] LED

);

wire [1:0] SEL;

assign SEL = { SW[0], PUSH };

assign SEL = { SW[0], PUSH };

assign LED[0] = (SEL==2'b00) ? SW[1] :

(SEL==2'b01) ? SW[2] :

SW[3];

```

endmodule

#### **Conditional operations**

- \* Think about circuit!

- \* Don't care is "x"

- \* For correctness:

- Write default value

- Check consistency of conditions

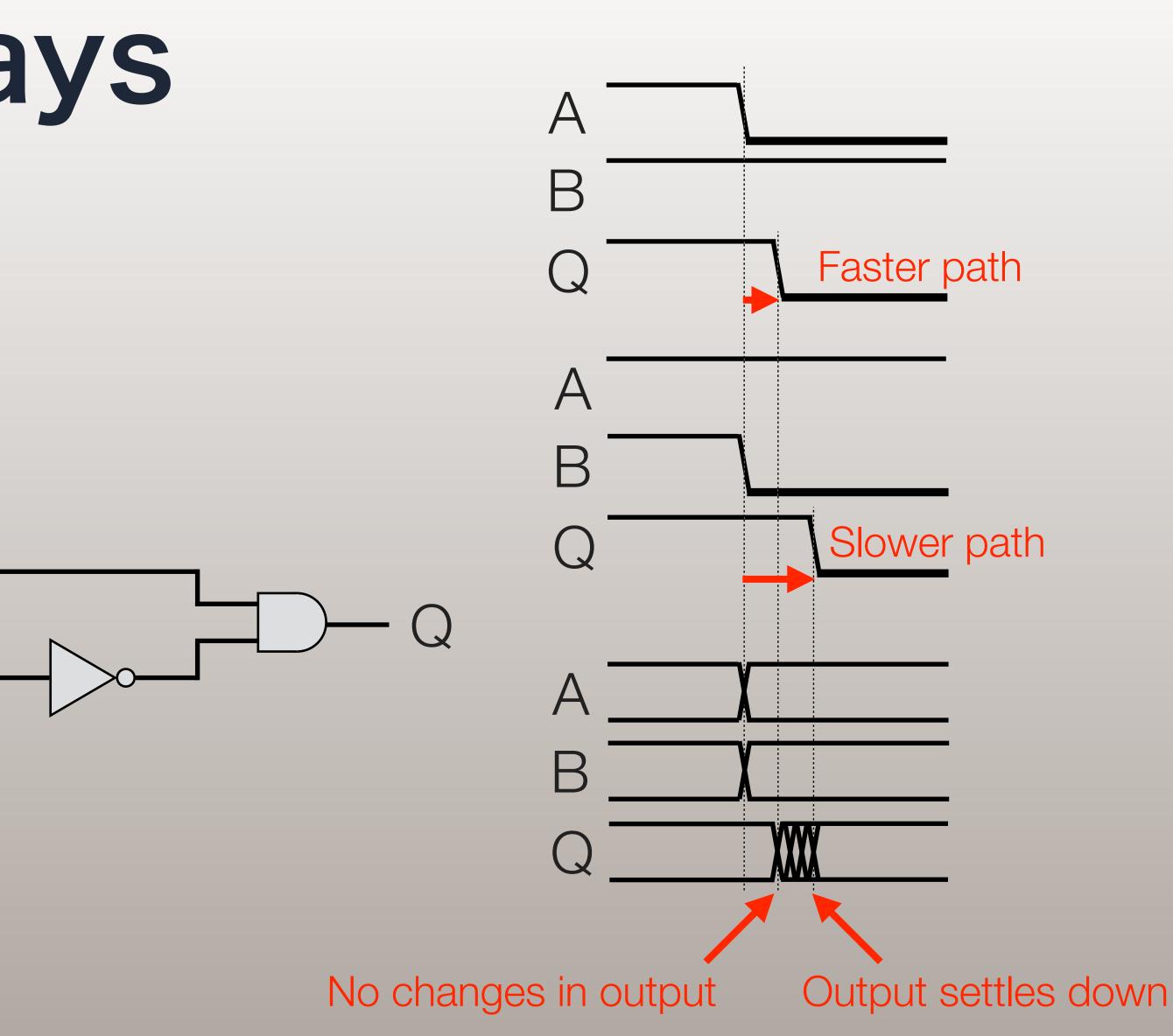

### Gates and Delays

- Input / Output transitions

- Gate and wire delay

- Different input causes different delay time B

- Contamination delay and Propagation delay

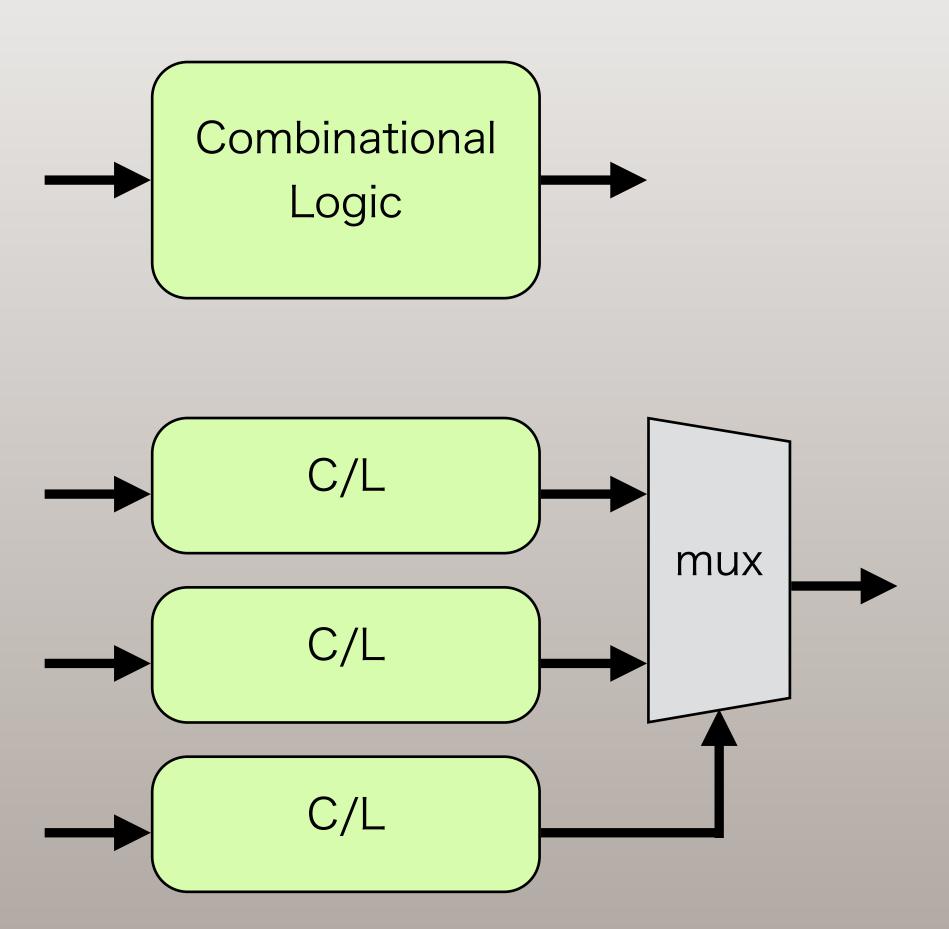

# Think about resulting circuit

Condition affects on # inputs of MUX and # MUX stages

### All above is about "Internals"

Thinking about "inside" of the FPGA is not sufficient Let's see signal pins of the FPGAs

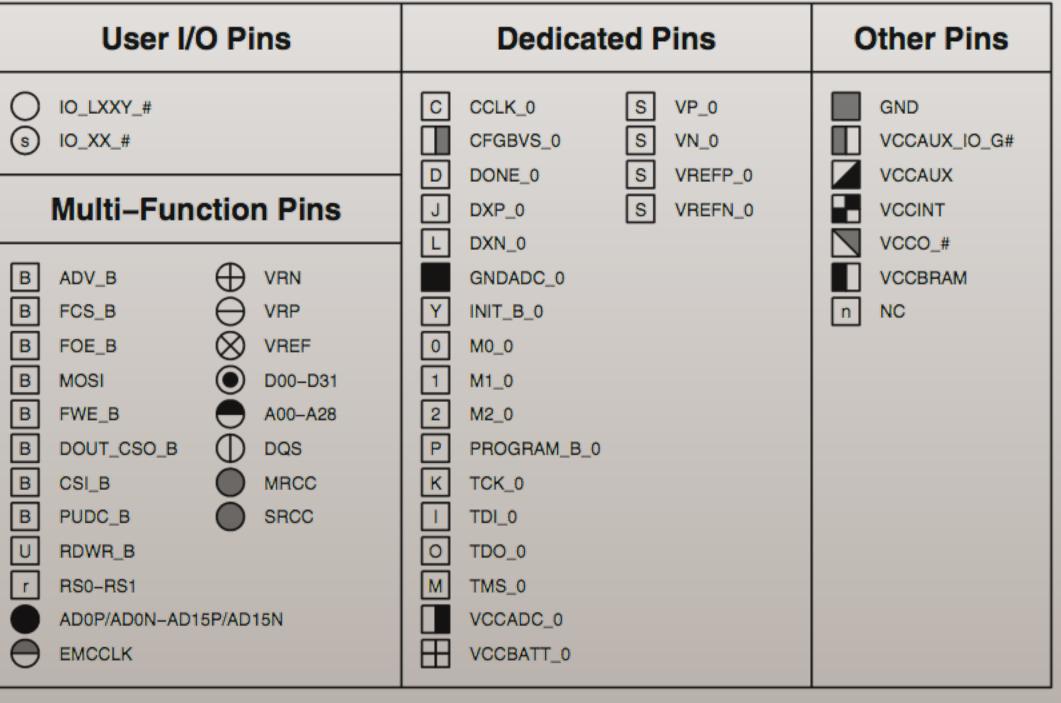

# FPGA is general-purpose

- Some flexibility of using signal pins

- \* "Dedicated" pins such as power supplies and startup

- "User I/O" pins that are fully programmable

- "Multi-purpose" pins for user I/O but some special capability such as clock inputs

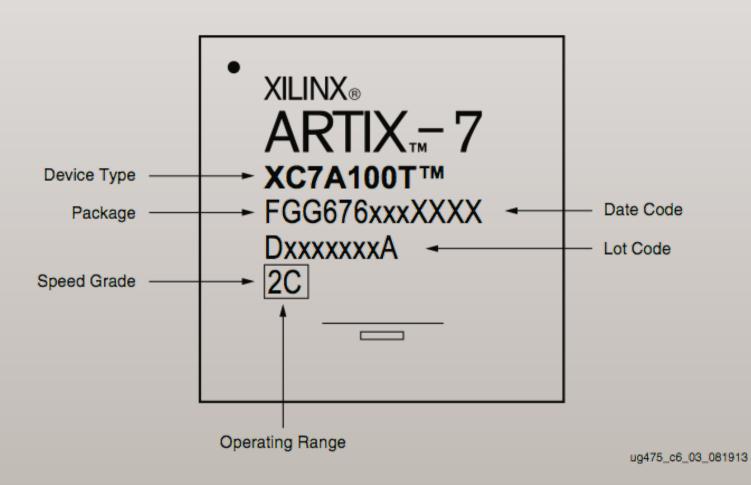

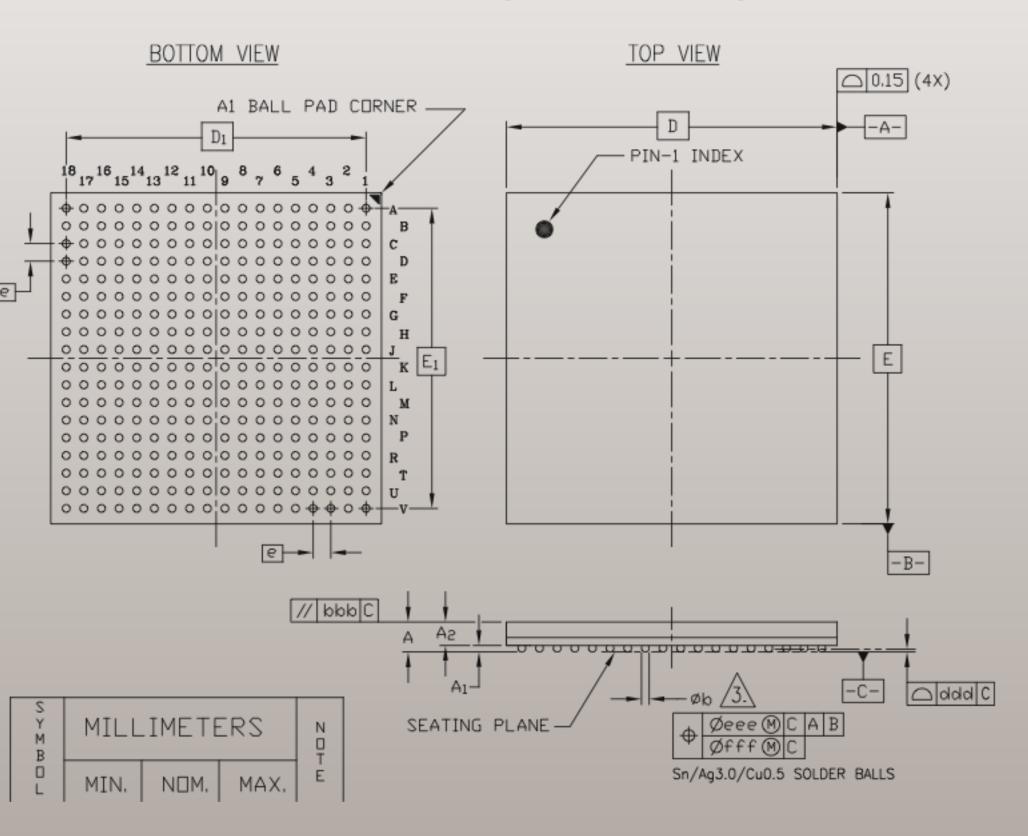

# Front and back of the chip

Xilinx UG475より

BGA (Ball Grid Array) is popular: pins are regularly arranged solder balls

#### CS/CSG324 and CS/CSG325 Wire-Bond Chip-Scale BGA Artix-7 FPGAs (0.8 mm Pitch)

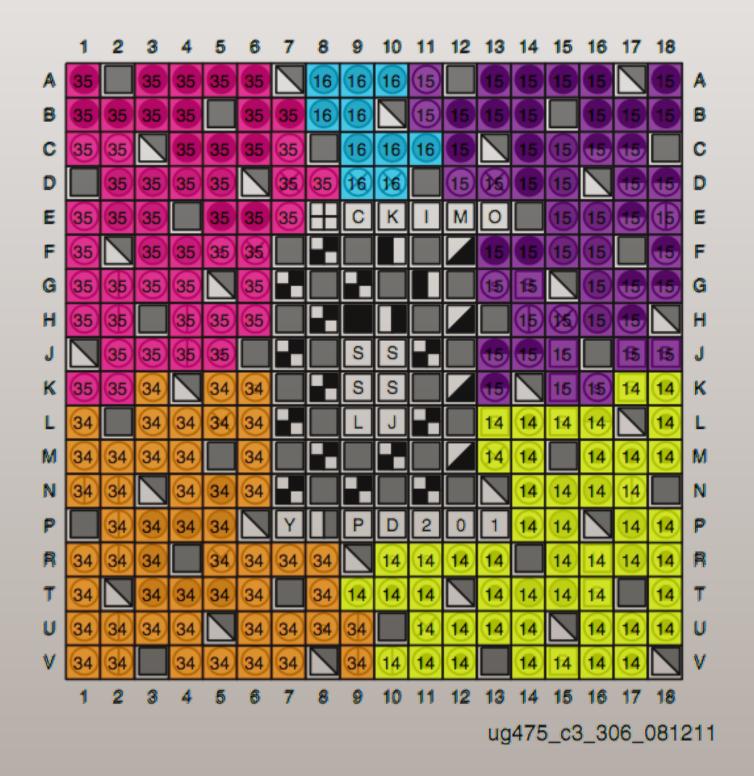

### Pin maps

Colored are user I/O pins, different colors are I/O banks

ug475\_c3\_305\_090711

# Pin arrangement and designer

- Required to read the data sheet carefully if:

- You're designing FPGA board

- Connecting something to board's GPIO (General Purpose I/O)

- Otherwise, we have to just know "what is connected to which pin"

- Using off-the-shelf board is (mostly) this

### Pin assignment: Schematics

### Pin assignemnt: Schematics

|             | IC8D                           |                    |

|-------------|--------------------------------|--------------------|

|             | BANK 34                        |                    |

| <u>R K6</u> | _                              | L1 AN6             |

| U8          | IO_0_34 IO_L1P_T0_34           | M1 AN7             |

|             |                                | K3 CE              |

|             | IO_L2P_T0_34                   | L3 CA              |

|             | IO_L2N_T0_34                   | N2 AN4             |

|             | IO_L3P_T0_DQS_34               | N1 CB              |

|             | IO_L3N_T0_DQS_34               | M3 AN2             |

|             | IO_L4P_T0_34                   | M2 CF              |

|             | IO_L4N_T0_34                   | K5 LEDI6 R         |

|             | IO_L5P_T0_34                   | L4 CD              |

|             | IO_L5N_T0_34                   | L6 CG              |

|             | IO_L6P_T0_34                   | L5 CC              |

|             | IO_L6N_T0_VREF_34              | UI LEDI3           |

|             | IO_L7P_T1_34                   | V1 LED10           |

|             | IO_L7N_T1_34                   | U4 SW8             |

|             | IO_L8P_T1_34                   | U3 LED9            |

|             | IO_L8N_T1_34                   | U2 SW10            |

|             | IO_L9P_T1_DQS_34               | V2 SW9             |

|             | IO_L9N_T1_DQS_34               | V5 SW7             |

|             | IO_L10P_T1_34                  | V4 LED8            |

|             | IO L10N T1 34                  |                    |

|             | IO_L11P_T1_SRCC_34             |                    |

|             | IO_L11N_T1_SRCC_34             | T3 SW11<br>T5 LED4 |

|             | IO_L12P_T1_MRCC_34             | T5 LED4<br>T4 LED5 |

|             | IO_L12N_T1_MRCC_34             | N5 AN3             |

|             | IO_L13P_T2_MRCC_34             | P5 LED12           |

|             | IO_L13N_T2_MRCC_34             | P4 SW15            |

|             | IO_L14P_T2_SRCC_34             | P3 SW14            |

|             | IO_L14N_T2_SRCC_34             | P2 LED15           |

|             | IO_L15P_T2_DQS_34              | R2 LED14           |

|             | IO_L15N_T2_DQS_34              | M4 DP              |

|             | IO_L16P_T2_34                  | N4 AN5             |

|             | IO_L16N_T2_34                  | R1 LED11           |

|             | IO_L17P_T2_34                  | T1 SW12            |

|             | IO_L17N_T2_34                  | M6 AN1             |

|             | IO_L18P_T2_34                  | N6 AN0             |

|             | IO_L18N_T2_34                  | R6 SW3             |

|             | IO_L19P_T3_34                  | R5 SW4             |

|             | IO_L19N_T3_VREF_34             | V7 SW5             |

|             | IO_L20P_T3_34                  | V6 SW6             |

|             | IO_L20N_T3_34                  | U9 SW0             |

|             | IO_L21P_T3_DQS_34              | V9 LED1            |

|             | IO_L21N_T3_DQS_34              | U7 LED6            |

|             | IO_L22P_T3_34<br>IO_L22N_T3_34 | U6 LED7            |

|             |                                | R7 SW2             |

|             | IO_L23P_T3_34<br>IO_L23N_T3_34 | T6 LED3            |

|             | IO_L23N_I3_34<br>IO_L24P_T3_34 | R8 LED2            |

|             | IO_L24P_15_34<br>IO_L24N_T3_34 | T8 LED0            |

|             | 10_12414_15_54                 |                    |

LED17 SW1

#### Constraints

- Pin assignments are not described by HDL

- Given to CAD tools as "implementation constraints"

- Independent file from HDL

- Pin number, voltage, clock frequency, etc.

### **XDC** constraints (Vivado)

module sw\_led input [3:0] SW, input PUSH );

set\_property PACKAGE\_PIN U9 [get\_ports SW [0]] set\_property PACKAGE\_PIN U8 [get\_ports SW [1]] set\_property PACKAGE\_PIN R7 [get\_ports SW [2]] set\_property PACKAGE\_PIN R6 [get\_ports SW [3]] set\_property IOSTANDARD LVCMOS33 [get\_ports {SW[\*]}]

set\_property PACKAGE\_PIN E16 [get\_ports PUSH] set\_property IOSTANDARD LVCMOS33 [get\_ports PUSH]

### UCF constraints (ISE: obsoleted)

```

module sw_led

input [3:0] SW,

input PUSH );

NET "SW[0]" LOC = U9;

NET "SW[1]" LOC = U8;

NET "SW[2]" LOC = R7;

NET "SW[3]" LOC = R6;

NET "SW[*]" IOSTANDARD = LVCMOS33;

NET "PUSH" LOC = E16 | IOSTANDARD = LVCMOS33;

```